5-1.Explanation of submodule(Input and output)

The submodule is a syntax to describe a hierarchical structure.

It is necessary to prepare two modules at least such as the higher one and the lower one

for creating a hierarchical structure.

Submodule declaration is implemented in a higher module.

And, the lower module to be a submodule is called “template”.

The submodule declaration specifies a “template” to make it substantial.

The template that was made substantial is called “instance”.

Creating “instance” of “template” makes the following, etc. possible.

– To input an arbitrary value to an data input terminal to an “instance”.

– To call a control input terminal of an “instance”.

– To receive a control output terminal of an “instance”.

Submodule syntax declares with the following method.

Name_of_template Name_of_instanceAnd, it is possible to prepare multiple “instances”

by delimiting the “instance” names with “,”.

Furthermore, it is also possible to specify the “multiplicity”

that creates multiple “instances” with the same name.

The “multiplicity” declares as follows.

Name_of_template Name_of_instance [Number_of_multiplicity]The number of multiplicity is expressed by the natural number.

Each terminal of the “instance” can be operated

from a higher module by using a submodule syntax.

And, it can implement the action such as passing a data from the “instance” to the higher module, etc

When each terminal like data and the control line etc.

of the instance is specified, it describes it as follows.

When it specifies each terminal such as a data and a control line, etc. of the “instance”,

it is described as follows.

Instance_name.Terminal_nameIt is possible to read out the value of an “instance” and to transmit the “instance” by using this.

Let’s see the following Example 31 as a usage example of the submodule syntax.

//the submodule sub_ex31

declare sub_ex31 {

input a[4], b[4] ;

output f[4] ;

}

module sub_ex31 {

f = a + b ;

}

//the top module ex31

declare ex31 {

input inA[4], inB[4] ;

output outF[4] ;

}

module ex31 {

//To instantiate the submodule "sub_ex30" with the name of SUB

sub_ex31 SUB ; //Expression 1

{

SUB.a = inA ; //Expression 2

SUB.b = inB ; //Expression 3

outF = SUB.f ; //Expression 4

}

}

|

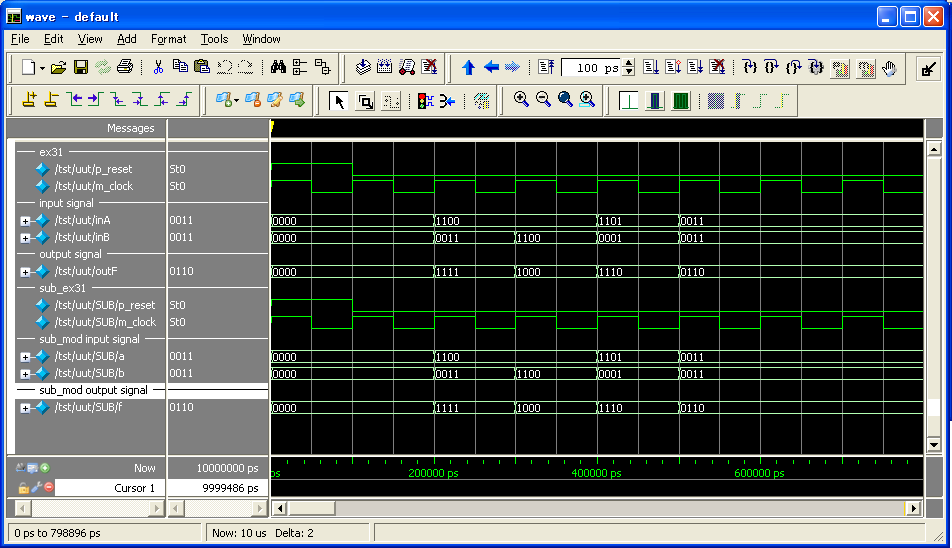

Example 31 consists of the top module “ex31″ and the submodule “sub_ex31″.

The “sub_ex31″ declares an instantiation as the name of SUB in the expression 1 in the “ex31″.

The expression 2 is an action that intends to assign “inA” to the data input terminal “a” of SUB.

The expression 3 is an action that intends to assign “inB” to the data input terminal “b” of SUB.

And, the expression 4 is an action that intends to assign the data output terminal “f” of SUB to “outF”.

So, let’s see the simulation result of Example 31.

5-2.Explanation of submodule(Control terminal)

Using a submodule syntax makes it possible to call the control terminal of “instance”.

To call the control terminal of “instance”, it is described as follows.

Instance_name.Name_of_control_input_terminal()And, it is described as follows

when the actual argument is given to the control input terminal of the “instance”.

Instance_name.Name_of_control_input_terminal(<Actual_argument1>, <Actual_argument2>, … <Actual_argumentX>)Please delimit it with comma “,” when multiple actual arguments are given.

And, the description method

when an output signal is received at the same time of calling a control input terminal is as follows.

Instance_name.Name_of_control_input_terminal(<Actual_argument>).Terminal_nameLet’s see the following Example 32 as a usage example of the control terminal of a submodule syntax.

//The submodule sub_ex32

declare sub_ex32 {

input a[4], b[4] ;

output f[4] ;

func_in exec_start(a, b) ;

func_out end_call(f) ;

}

module sub_ex32 {

wire w1[4] ;

function exec_start {

w1 = a + b ;

end_call(w1) ;

}

}

//The top module ex32

declare ex32 {

input inA[4], inB[4] ;

}

module ex32 {

reg result_reg[4] ;

reg r1=0, r2=0, r3=0 ;

//To instantiate the submodule "sub_ex32" with the name of U_SUB

sub_ex32 U_SUB ; //Expression 1

r1 := 0b1 ; r2 := r1 ; r3 := r2 ;

if(r1 & r2 & ~r3) U_SUB.exec_start(inA, inB) ; //Expression 2

if(U_SUB.end_call) result_reg := U_SUB.f ; //Expression 3

}

|

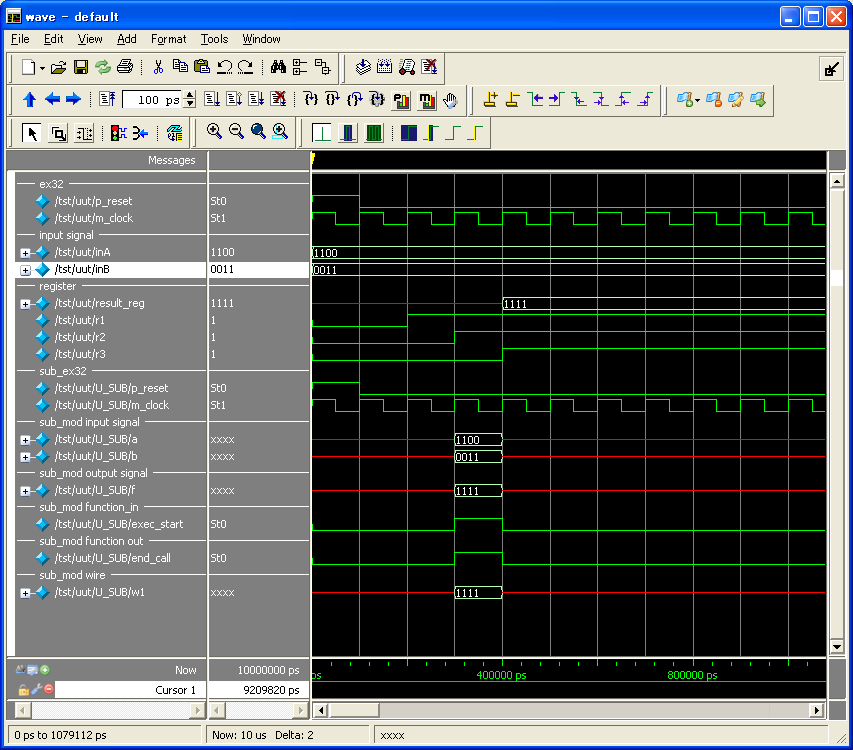

Example 32 is an example to use a control terminal in the submodule.

Example 32 consists of the top module “ex32″ and the submodule “sub_ex32″.

First, in the expression 1 in ex32, “sub_ex32″ is instantiated with the name of U_SUB.

In the expression 2, when the “if” syntax is true,

it calls the control input terminal “start” of U_SUB, to which the argument of 1 was given.

And, the expression 3 is an action

that assign the data output terminal of U_SUB “f” to the register “reg_buff”

if the control output terminal “end_call” of U_SUB is true in the conditional syntax of “if”.

So, let’s see the simulation result of Example 32.

5-3.Explanation of submodule(Parameter passing)

Declaration of parameter

It explains the parameter passing that uses a submodule syntax.

When a hierarchical structure of a higher module and a lower module was made,

the parameter syntax is used for passing the parameter from the higher to the lower.

The parameter is the set value when a lower module is made.

It becomes possible to change the state when being activated

by passing an arbitrary parameter to the lower module.

The parameter syntax can be used to create “A module of which source code is not disclosed”, etc.

Also, the parameter of a module declares in a “declare” syntax,

and the two kinds of the integer value type and the character string type can be used.

Declaration example of the parameter

param_int Parameter_name // Integer value type parameter

// Signed 32bit integerparam_str Parameter_name // Character string type parameter

// No limitation. It depends on the memory of the processing environment.

Let’s see the following Example 33 as a usage example of the parameter syntax.

// "test_sub" to be a lower module

declare test_sub {

// Declaration of parameter

param_int A, B ; // Declaration of the integer value type parameter A and B

param_str C ; // Declaration of the character string type parameter C

input in_A ;

input in_B ;

}

module test_sub {

// Declaration part of internal structure element

// Part of operation description

}

// ex32 to be a higher module

declare ex33 {

// Input/output structure element

}

module ex33 {

// Submodule declaration of internal structure element

test_sub SUB1(A=15, B=22, C = "NEKO") ; // Declaration by passing the prameter to the submodule

test_sub SUB2 ; // Single submodule declaration

test_sub SUB3, SUB4 ; // Multiple submodule declarations

// Part of operation description

}

|